На протяжении почти всей истории полупроводниковой промышленности производители чипов стараются уменьшить размеры транзисторов и их элементов, потому что это дает несколько преимуществ. Во-первых, меньший размер транзистора позволяет быстрее переключать его состояния и тратить на это меньше энергии. Благодаря этому повышается общая энергоэффективность чипа, что зачастую напрямую отражается на важных для потребителя свойствах, например, позволяет увеличить длительность работы от одного заряда аккумулятора. Во-вторых, при меньшем размере транзистора на одной полупроводниковой пластине можно разместить больше чипов. Кроме того, это уменьшает время, требуемое на прохождение сигнала между компонентами чипа.

Традиционно техпроцесс в чипах принято называть в нанометрах. Однако если раньше этот параметр нес конкретный физический смысл, как правило, отражая длину затвора или размер наименьшего компонента в транзисторе, то уже довольно давно этот термин не привязан к какой-либо конкретной величине и фактически превратился в маркетинговое название.

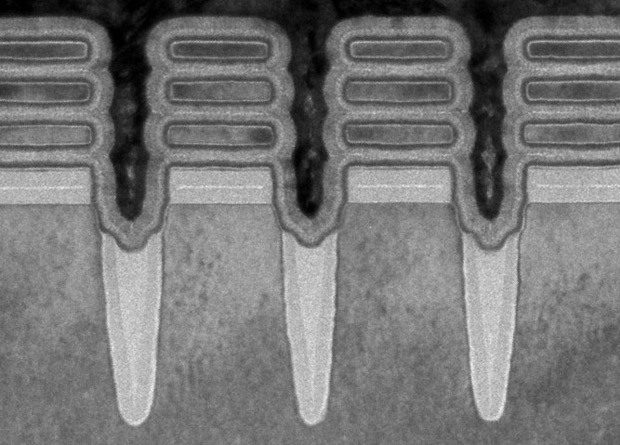

Компания IBM, которая сама не производит чипы, но активно ведет разработки в этой области и лицензирует технологии другим производителям, объявила о создании первого тестового чипа, выполненного по 2-нанометровому техпроцессу. В новом техпроцессе используется архитектура GAA (Gate-all-around), при которой затвор транзистора окружает канал со всех сторон. В реализации IBM канал состоит из трех пластин, расположенных друг над другом и имеющих толщину (высоту) в 5 нанометров. Длина канала составляет 12 нанометров.

В пресс-релизе компания отмечает, что новый техпроцесс позволит добиться на 45 процентов большей производительности или на 75 процентов меньшего энергопотребления, чем лучшие из существующих сегодня 7-нанометровых чипов. При этом неизвестно, о техпроцессе какого производителя идет речь.

Учитывая, что название техпроцесса в нанометрах на сегодняшний день почти не несет смысловой нагрузки, наилучший показатель для сравнения между собой техпроцессов разных производителей — это плотность транзисторов на пластине. Как отмечает AnandTech, судя по приводимым IBM данным, плотность их техпроцесса составляет 333,33 миллиона транзисторов на квадратный миллиметр. Для сравнения, 3-нанометровый техпроцесс TSMC (пока не используется в серийном производстве) позволяет добиться плотности в 292,21 миллиона на квадратный миллиметр, а при 7-нанометровом техпроцессе от Intel (тоже находится в разработке) плотность достигает 237,18 миллиона на квадратный миллиметр.

IBM разрабатывает не только архитектуры для классических чипов, но и квантовые компьютеры. В 2017 году она представила компьютер, работающий с 50 кубитами, а в 2020 представила и предоставила сторонним компаниям 65-кубитный квантовый компьютер.

Фото: Снимок нового чипа, сделанный на просвечивающем электронном микроскопе. IBM

Комментарии:

Авторизуйтесь, чтобы оставить отзыв